Қазақстан Республикасы Тәуелсіздігінің 30 жылдығына арналған «Сейфуллин оқулары — 17: «Қазіргі аграрлық ғылым: цифрлық трансформация» атты халықаралық ғылыми — тәжірибелік конференцияға материалдар = Материалы международной научно — теоретической конференции «Сейфуллинские чтения — 17: «Современная аграрная наука: цифровая трансформация», посвященной 30 — летию Независимости Республики Казахстан.- 2021.- Т.1, Ч.3 - С. 62 - 65

## АППАРАТНО-ПРОГРАММНАЯ РЕАЛИЗАЦИЯ ЛИНЕЙНЫХ АВТОМАТОВ

Шокаев С.Б., Хамзина Б.Е., Жолдангарова Г.И.

В данной статье представлена разработанная схема линейного автомата для защиты отладочной платы от перегрузки и короткого замыкания актуальная для задач техники безопасности человека. Схема реализуется на отладочной плате Cyclone V с помощью платформы Quartus II.

*Ключевые слова:* сумматор, линейный автомат, умножитель, код полинома, программатор.

Короткое замыкание — частое явление в любых электроприборах, и оно может вызвать серьезные проблемы и нести опасность жизни человека. При значительном увеличении силы тока, которое происходит при коротком замыкании, выделяется большое количество теплоты в проводниках, что вызывает разрушение изоляции и возгорание. Поэтому, чтобы защитить линии устанавливают линейные автоматы, но их размеры слишком большие для установки их на малогабаритные устройства связи. Поэтому, для повышения производительности линейных автоматов нами был разработан программный код линейных автоматов на плате Cyclone V. В качестве наилучшего средства структуризации аппаратно-программной реализации линейных автоматов мы использовали алгоритмическую конструкцию, близкую к конструкции сложных устройств наподобие синтезаторов частот с целью объединения отдельных фрагментов в исходной неструктурированной ГСА.

Линейный автоматы с устройствами защитного отключения защищают как процессор отладочной платы, так и все устройство от перегрузки и короткого замыкания, а также людей и животных от поражения электрическим током.

В схеме с линейными автоматами разрешается использовать только линейные элементы, выполняющие операции сложения и умножения по модулю простого числа q.

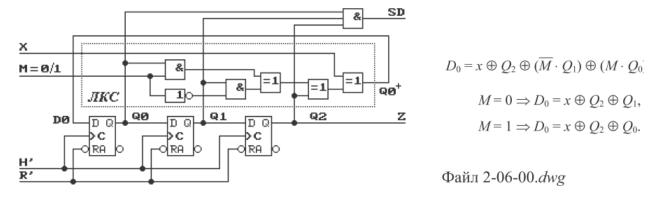

При разработке линейных автоматов на отладочной плате использовался математический вид линейного автомата над полем GV(2)(рисунок 1)[1].

$$F(x) = a_n x^n + a_{n-1} x^{n-1} + \dots + a_p x^p + \dots + a_1 x^1 + a_0 x^0$$

Рисунок 1. Многофункциональный линейный автомат над полем GF(2)

Последовательная интерпретация входных сигналов позволяет поставить задачу синтеза линейных автоматов над полем GF(q), выполняющих умножение и деление полиномов.

Последовательность входного сигнала x на линейный автомат в виде логических 1 и 0 называется единичным импульсом (рисунок 2), а изменениме сигнала линейного автомата - импульсной функцией [2].

Рисунок 2. Реакция линейного автомата над полем GF(2) на единичный импульс

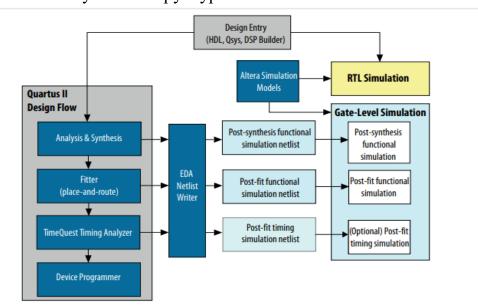

Разработанная нами схема была создана на платформе Quartus II, которая позволяет строить на основе Verilog HDL модели и преобразовывать ее в схема на уровне простых логических элементов[3].

Нами была разработана Verilog HDL модель линейного автомата для платформы Quartus II. На языке программирования был создан отдельным скриптом умножитель и отдельно сумматор, созданна библиотека по данным скриптам, после уже использовались данные библиотеки как отдельные логические функции (рисунок 3).

```

Dmodule Adder_Behavioral_Verilog(

input X1, X2, Cin,

output S, Cout

);

reg[1:0] temp;

always @(*)

begin

temp = {1'b0,X1} + {1'b0,X2}+{1'b0,Cin};

end

assign S = temp[0];

assign Cout = temp[1];

endmodule

```

Рисунок 3. Verilog HDL модель линейного автомата.

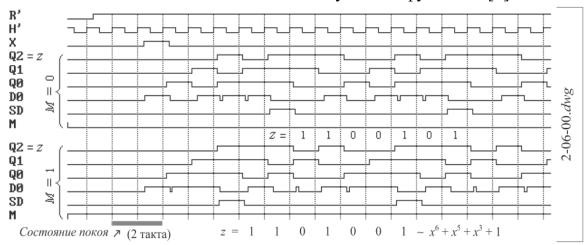

Данная Verilog HDL модель позволяет реализовать линейный автомат в виде алгоритма и загрузить на отладочную плату. После реализации линейных автоматов на отладочной плате был создан тестовый файл для проверки кода линейного автомата в виде подачи входных сигналов 1 и 0. При помощи пакета ISIM мы получили временную диаграмму, которая показывает что линейный автомат работает правильно. (рисунок 4).

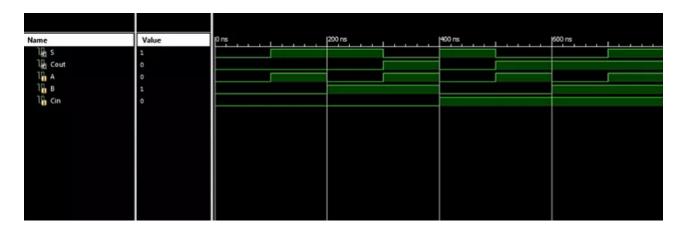

С помощью платформы Quartus II была построена схема линейного автомата на уровне умножителей.(рисунок 5). Данный умножитель отвечает за основную работу самого линейного автомата, умножает два и более входных сигнала и в зависимости от полученного результата будет наше выходное значение самого линейного автомата.

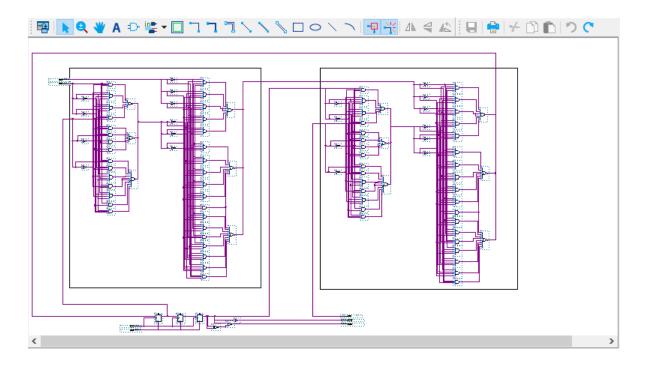

Для создания и тестирования смоделированной схемы был использован пакет ISIM от платформы Quartus II, с помощью алгоритма на котором она построена (рисунок 6) [4].

Рисунок 4. Временная диаграмма сумматора

Рисунок 5. Структурная схема линейного автомата

Рисунок 6. Алгоритм моделирования схемы на платформе Quartus II

Таким образом, нами была разработана схема линейного автомата для защиты отладочной платы от короткого замыкания и перегрузки и безопасности жизнедеятельности человека. Данная схема была построена в виде Verilog HDL модели и протестирована с помощью платформы Quartus II.

Список литературы

- 1. Пухальский Г.И., Новосельцева Т.Я. Проектирование цифровых устройств: Учебное пособие. СПб.: Издательство «Лань». 2012. 896 с.

- 2. Стемпковский А.Л. Методы логического и логико-временного анализа цифровых КМОП СБИС/А.Л. Стемпковский, С.В. Гаврилов, А.Л. Глебов; под общ. Ред. А.Л. Стемпковского; Институт проблем проектирования в микроэлектронике РАН. М.: Наука, 2007. 220 с.

- 3. Cyclone V Device Overview. Latest document on the web: Intel, 2018

- 4. <u>Hameed, A.S., Kathem, M.J.</u>. <u>High speed modified carry save adder using a structure of multiplexers</u> [Электронный ресурс Scopus]. (Дата обращения: 20.09.2020).